SEEQC’s Chip-Based Quantum Architecture

SEEQC builds the control system into the chip stack, not in a rack across the lab. That flips the usual picture: fewer cables, less heat, and shorter feedback loops. Put the control where the qubits live, and everything gets simpler.

System-On-A-Chip Integration For Quantum Control

SEEQC folds clocking, pulse generation, feedback, and routing into a chip-level platform that sits inside the cryostat. Instead of long analog paths and dozens of coax lines, you get tight timing and digital configurability right next to the qubits. It’s still engineering, not magic, but the wiring headache eases a lot.

Key points:

- On-chip timing and digital logic cut round-trip delay for calibration and feedback.

- Localized control trims analog drift and crosstalk that creep in over long cables.

- Firmware updates change behavior without ripping up hardware.

- Heat-sensitive stages see less load because most signaling is digital and compact.

Typical placement (illustrative):

| Cryo stage | Approx. temp | What goes here | Why it matters |

|---|---|---|---|

| Room temp | ~300 K | Host CPU/GPU, control software | High-level orchestration and compilation |

| 4 K | ~4 K | Digital interfaces, serializers, memory buffers | High-bandwidth links into the fridge |

| 1 K | ~1 K | Conditioning, isolation, some digital fan-out | Reduces noise before the coldest stage |

| mK plate | ~10–100 mK | Qubits, near-qubit drivers/readout front-ends | Short paths, low latency, low noise |

Digital Readout And Multiplexing Inside Cryogenic Stages

Instead of hauling raw analog signals up the stack, SEEQC digitizes and processes readout close to the qubits. Local demod, thresholding, and counters turn messy waveforms into crisp bits. Then a handful of fast lanes carry many channels out of the fridge.

What this changes:

- Frequency, time, and code multiplexing reduce the number of feedthroughs.

- Digital packetization keeps signal integrity and slashes analog complexity.

- Fast local classification speeds up reset and mid-circuit feedback.

- Cal data (IQ histograms, error flags) can be streamed without extra analog paths.

Example channel count (illustrative):

| Configuration | Qubits | Cryostat feedthroughs for readout |

|---|---|---|

| Discrete analog lines | 64 | ~64 coax |

| In-cryostat digital mux | 64 | ~8–16 high-speed lines |

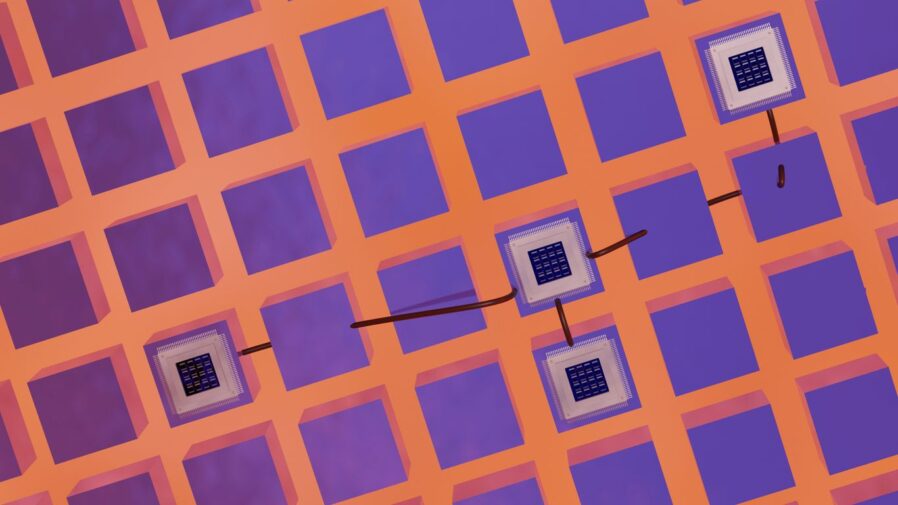

Modular Multi-Chip Modules For Rapid Iteration

SEEQC packages the qubit die with control and readout chiplets in a single module. If a new driver or filter comes along, swap that tile and keep the rest. Lab teams get to test ideas in weeks, not quarters.

Why the module approach helps:

- Mix-and-match: qubit die + control chiplet + readout chiplet on one interposer.

- Short, repeatable interconnects (micro-bumps, superconducting traces) keep timing tight.

- Yield and serviceability improve because subsystems can be upgraded independently.

- Faster bring-up: standard power, clock, and data pinouts across module revisions.

In practice, this means a clear path from a small qubit tile to larger arrays without rethinking the whole stack each time. You keep the digital plumbing, tune the quantum layer, and move on to the next build.

Single Flux Quantum Logic Powering SEEQC

Single Flux Quantum (SFQ) is the digital backbone of SEEQC’s approach. Instead of long, power-hungry microwave tones, SFQ uses tiny quantized pulses created by Josephson junctions. These pulses are fast, consistent, and stingy with energy. SFQ lets SEEQC run qubit control with orders-of-magnitude less energy than analog microwave chains.

SFQ logic sits cold, close to the qubits, so signals don’t slog through meters of cable. That cut in distance trims delay and slashes heat that would otherwise creep into the fridge. It also means timing is tighter and more predictable, which is exactly what you want when you’re stacking thousands of gates.

Energy-Efficient Control That Minimizes Thermal Load

Heat limits how many qubits you can wire up. Every coax, every attenuator, and every amplifier adds up. SFQ tackles this in three simple ways:

- Pulse-based control: fire only when needed, no continuous carriers.

- In-fridge digital logic: shorter runs, fewer cables, far less conduction into cold stages.

- Aggressive multiplexing: more channels per line without big analog overhead.

Quick comparison:

| Metric | SFQ control (in-cryostat) | Conventional microwave control |

|---|---|---|

| Timing granularity | ~1–10 ps | ~1–10 ns |

| Energy per event | ~1e-19 J per pulse | ~1e-13–1e-12 J per gate |

| Typical cable run | millimeters–centimeters | 5–20 meters |

| Electronics temperature | ~3–4 K (logic), mK (qubits) | ~300 K (racks) |

What this means in practice: less heat dumped into the mK stage, fewer thermal bottlenecks, and more room to grow qubit counts without the wiring nightmare.

Picosecond-Level Switching For Scalable Qubit Operations

Josephson junctions switch insanely fast. We’re talking picoseconds, not nanoseconds, which changes the playbook.

- High-speed scheduling: clocks in the tens to hundreds of GHz keep gate timing tight across many channels.

- Low-latency feedback: conditional resets, mid-circuit measurements, and quick retries can happen inside the fridge.

- Cleaner synchronization: picosecond-class jitter keeps parallel operations aligned without heavy analog calibration.

Put simply, faster control loops mean you can run more complex circuits before errors pile up, and you waste fewer cycles waiting on round trips to room temperature gear.

Digital Electronics Without Transistors In Superconducting Logic

SFQ is digital, but it’s not CMOS. There are no transistors switching voltages high and low. Instead, logic states are represented by the presence (or absence) of a single flux quantum pulse.

How an SFQ gate works, in a nutshell:

- A superconducting loop stores quantized magnetic flux.

- A Josephson junction toggles and emits a standard-size pulse when the logic condition is met.

- Pulses ripple through pipelines, counters, muxes, and readout blocks—just like bits—but with almost no static power at cryogenic temperatures.

This style of digital design brings a few handy perks:

- Deterministic pulse sizes make timing and calibration simpler over time.

- Static power can be near-zero with modern SFQ variants, which keeps the fridge happy.

- Programmable control: firmware can reshape pulse patterns for different qubits, gates, or calibration routines without reworking analog hardware.

Bottom line: SFQ turns qubit control into a cold, fast, fully digital workflow. You get tight timing, tiny energy per operation, and a clear path to scale without drowning the refrigerator in heat.

SEEQC’s Cryogenic Integration Bridging Quantum And Classical

Qubits need near‑zero heat and near‑zero delay, yet most control hardware sits meters away at room temp. That’s a mismatch. Put the brains next to the qubits and you cut delay, heat, and cost all at once. It sounds simple on paper, but it took purpose‑built superconducting logic and careful engineering inside the fridge to make it real.

Co-Located Control Chips Within The Refrigerator

SEEQC places digital control and readout silicon—built with superconducting Single Flux Quantum (SFQ) logic—inside the cryostat. In practice, many functions live at the 3–4 K stage, while latency‑sensitive triggers and readout helpers can sit even closer to the qubit plane.

- Short paths: millimeters or centimeters instead of meters of coax, so commands land on time.

- Less analog overhead: fewer mixers, fewer warm DAC/ADC links, and fewer drifting calibrations.

- Lower heat: picosecond SFQ pulses move bits with tiny energy, which keeps the cold stages stable.

- Tighter timing: co‑located clocks and triggers keep skew predictable across many qubits.

Low-Latency Digital Interfaces Replacing Analog Bottlenecks

Analog chains introduce drift, amplitude noise, and long round‑trip delays. SEEQC swaps that for digital chip‑to‑chip links: packetized control, deterministic triggers, and digital readout decisions made inside the fridge. Error‑correction loops—normally starved by latency—get the budget they need. Mid‑circuit measurements can feed right back into new pulses without waiting on a room‑temp path.

There’s also a nice side effect: this approach plays well with emerging photonic methods. Work on guiding light at unusual effective indices, like recent research on zero-index materials, hints at even tighter optical control that could complement cryogenic digital links down the road.

| Path | Typical round‑trip latency | Aggregate bandwidth to qubit plane | Notes |

|---|---|---|---|

| Room‑temp analog chain | 1–10 µs | 1–5 GSa/s per channel | Long cables, drift, frequent IQ re‑calibration |

| Cryogenic digital link | 10–100 ns | 10–40 Gbps per link | Deterministic timing, packetized control, closer to qubits |

Expanded Qubit Counts Through Reduced Wiring Overhead

The “forest of cables” limits scale. Every coax adds heat load, space, and cost. SEEQC trims this by performing fan‑out, switching, and multiplexing inside the cryostat, so one high‑speed digital link can manage many qubits instead of one line per control.

- In‑fridge multiplexing: combine time, frequency, and digital addressability to share lines.

- Digital fan‑out trees: local routers distribute triggers and waveforms to dozens of channels.

- Readout on board: thresholding and compression reduce data volume before it leaves the fridge.

- Calibrations that stick: shorter, colder paths drift less, so large systems stay in spec longer.

Net result: fewer penetrations through the refrigerator, lighter thermal load at the mixing chamber, and a path to much larger qubit counts without the usual cable spaghetti.

SEEQC Prism: Full-Stack Firmware And Software

Prism is the software-and-firmware stack that turns SEEQC’s cryogenic digital logic and SFQ co‑processors into something developers can actually program and run at scale. It covers the path from high‑level circuits down to timing-safe microcode, with monitoring, calibration, and feedback built in. It’s practical, not pretty: fewer analog quirks, more deterministic clocks, and a clear way to move fast without cooking the fridge.

Enabling Cryogenic Logic And SFQ Co‑Processors

Prism speaks the native language of cryogenic chips. Think packetized gate programs, picosecond-aligned schedules, and low‑latency feedback that stays inside the refrigerator when it matters.

- Deterministic timing tied to SFQ clocks (ps–ns windows) with bounded jitter

- In‑fridge drivers for SFQ multiplexers, digital readout, and cryoCMOS blocks

- Fast feedback hooks for reset, mid‑circuit measurement, and basic error handling

- Versioned bitstreams and safe rollback for cryo firmware updates

- Health probes: temperature, timing drift, readout histograms, and link status

| Layer | Location | Time scale | What it controls |

|---|---|---|---|

| Firmware microcode | 20–100 mK | ps–ns | SFQ pulse trains, switches, on‑chip multiplexers |

| Real‑time runtime | 3–4 K | ns–µs | gating, readout thresholding, demod, feedback loops |

| Host services | Room temp | ms+ | compilation, orchestration, logging, experiment management |

This split keeps the fast stuff near the qubits while leaving heavy tasks topside. Less cabling drama, fewer conversion stages, and a cleaner control loop.

Reference Platforms And Tooling For Application Development

You don’t start from a blank page. Prism ships with reference systems, sample pipelines, and drivers that match SEEQC hardware, so teams can stand up experiments without hunting for missing pieces.

- SDK with Python APIs, CLI, and notebook templates; device profiles for supported chips

- Compiler passes for gate set mapping, resource‑aware scheduling, and timing quantization

- Hardware emulators and simulators that mirror SFQ timing and cryogenic constraints

- Calibration service: automated sweeps, fitters, and drift alerts

- Artifact tracking: configs, binaries, logs, and datasets linked to each run

Suggested workflow:

- Write circuits in your favorite framework or Prism’s DSL. 2) Compile to the target profile and check constraints. 3) Validate on the simulator with live noise models. 4) Run on hardware with real‑time metrics. 5) Auto‑calibration closes the loop and updates the profile.

Support For Simulation, Optimization, And Machine Learning

Prism leans into noise‑aware development and tight experiment loops. If you’re tuning a variational circuit or testing an optimizer, the stack keeps the hardware model and your code in sync.

- Device‑aware simulators: amplitude/phase damping, readout errors, and crosstalk models

- Optimizers: gradient‑based, SPSA, Bayesian, and coordinate search; early‑stop rules

- ML hooks for PyTorch/JAX to batch parameter updates and stream results

- Error‑mitigation utilities (zero‑noise extrapolation, measurement mitigation)

- Batch runners for sweeps, A/B tests, and long‑running studies with resumable jobs

Data from each shot lands in a tidy record: parameters used, calibration state, and raw/processed outcomes. That means you can reproduce a result next week, not guess what changed overnight.

Heterogeneous Computing With SEEQC And NVIDIA

SEEQC is building a stack where quantum chips don’t sit off to the side. They sit in the flow with GPUs and CPUs, sharing fast paths for data and tight timing. That’s the only way hybrid workloads stop feeling like science projects and start acting like systems you can scale and maintain.

Tight Coupling Of QPUs, CPUs, And GPUs

In this setup, each processor does what it’s good at: the QPU runs gates and readout, GPUs chew through linear algebra and decoding, and CPUs coordinate the show. The trick is avoiding copies, jitter, and surprise latencies that wreck control loops. The goal is simple: keep compute and data close to the qubits, and move fewer bytes further.

What “tight” actually looks like:

- Shared timing references and deterministic triggers between cryogenic control and host.

- Zero-copy or near-zero-copy moves (DMA/GPUDirect-style paths) into GPU memory.

- Compact binary payloads for readout/feedback instead of chatty control messages.

- Batched shots with fixed layouts so kernels stay hot and predictable.

- Fused GPU kernels for decoding + parameter updates to skip round trips.

Real-Time Error Correction With High‑Bandwidth Links

Error correction loops are unforgiving. Syndrome data needs to leave the cryostat, get decoded, and come back with a control action fast. Digital interfaces inside the fridge help by cutting analog overhead and jitter. On the host side, ring buffers, time-stamps, and backpressure keep the pipe steady when you push shot rates higher.

Indicative targets for a practical control path (non-binding, workload-dependent):

| Path | Latency budget (order) | Sustained throughput (order) | Typical role |

|---|---|---|---|

| QPU → cryogenic digital logic | sub-µs | tens of Gbps | Stream readout bits, trigger lines |

| Cryogenic stage → host memory | few µs | 10–100 Gbps | DMA batches of syndromes and metadata |

| Host CPU ↔ GPU | sub- to few µs | 100+ Gbps | Run decoders, filters, and updates |

A few tactics that pay off:

- Use fixed-size frames for syndrome streams so the decoder can be pre-planned.

- Keep a persistent GPU kernel alive to avoid launch overhead on every shot.

- Apply early-out rules when confidence is high, then skip unnecessary feedback.

Accelerated Hybrid Algorithms For Enterprise Workloads

Most real workloads are loops: prepare state on the QPU, measure, update on the GPU/CPU, repeat. Think VQE, QAOA, and quantum ML. Performance comes from overlap—let the QPU sample the next batch while the GPU digests the last one.

Practical patterns that reduce wall-clock time:

- Asynchronous pipelines: QPU sampling, GPU decoding, and CPU orchestration in parallel.

- Mixed-precision math on GPUs for gradient steps when accuracy budgets allow.

- Parameter caching and reuse across shots to cut host traffic.

- Topology-aware batching so circuits match qubit layout and reduce swaps.

- Telemetry in the loop (temperature, link stats) to auto-tune shot sizes and pacing.

If you stitch these pieces together, you get a system that feels less like a lab bench and more like a real compute node—fast paths, predictable timing, and headroom to grow the qubit count without drowning in cables or copies.

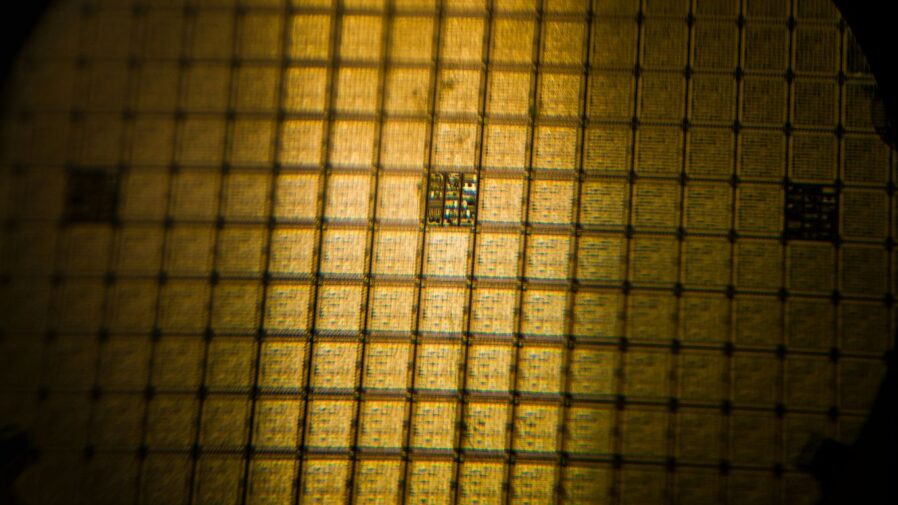

Fabrication Strength At SEEQC’s Superconducting Foundry

The Elmsford fab keeps the loop from idea to cold-tested hardware short, because design, fabrication, and cryogenic test sit under one roof. It’s practical, a little gritty, and focused on what actually moves qubits and control chips from CAD to the cryostat without drama.

Multi‑Layer Superconducting Chip Manufacturing In Elmsford

SEEQC builds stacked superconducting circuits that mix SFQ logic, resonators, and control features on the same wafer. The flow looks familiar—thin‑film deposition, junction definition, patterning, and passivation—but it’s tuned for low loss and uniform junction behavior.

- Multi-layer metal stacks with reliable crossovers and vias for routing dense control networks.

- Tight control of Josephson junction variation across a wafer for predictable bias points.

- Dielectrics and interfaces chosen to curb microwave loss and two‑level defect noise.

- In‑line monitors and parametric structures that flag drift early, before a full run is at risk.

- Rapid re‑spins of masks for small tweaks, so designs can iterate without long pauses.

If you’ve ever waited months for a mask change, you know why this matters. Here, process recipes and layout rules are co-owned by the same team that has to make the parts work at 10 millikelvin.

Vertically Integrated Design, Test, And Packaging

The same people who tape out the chips also plan how they’re tested and packaged. That sounds obvious, but it prevents so many late surprises.

- Design-to-fab handoff uses a superconducting PDK and SFQ cell libraries that match what the tools actually build.

- Wafer- and die-level test includes room‑temp proxies and targeted cryogenic probing for junction I‑V, resonator checks, and SFQ timing.

- Packaging aligns with cryostat realities: low‑outgassing materials, clean thermal paths, and short interconnects for low latency.

- Flip‑chip and indium-bump options for marrying qubit dies to control/readout chips with minimal parasitics.

- Feedback is fast: test data rolls straight into the next mask update, not a slide deck that sits for a quarter.

In practice, this cuts down on the "works in simulation, fails in the fridge" problem that haunts mixed quantum‑classical stacks.

Proven Pathways From Lab Concepts To Deployed Systems

Getting from a sketch to something a customer can run overnight is more than yield. It’s a playbook.

- Stage gates: concept vehicles → engineering runs → pilot modules → fieldable systems, with checklists at each step.

- Reliability screens: repeated cryo cycles, bias stability checks, connector wear, and vacuum compatibility audits.

- Traceability: lot histories, calibration data, and versioned firmware images tied to each module.

- Reference designs: known‑good SFQ control blocks, readout chains, and interposer layouts to start projects on firm ground.

- Serviceability: fixtures and packaging that can be swapped or upgraded without tearing apart a fridge.

No magic, just a factory rhythm tuned for superconducting logic and quantum hardware. The result is a clearer path from lab demo to something you can actually deploy and maintain.

SEEQC’s Universal Compatibility Across Qubit Modalities

SEEQC builds its control stack to speak the native language of any qubit, not the other way around. Different qubit types expect different signals, timing, and readout paths. Instead of forcing one style on everyone, SEEQC maps its digital, chip‑based control to whatever the hardware needs—microwave bursts for superconductors, fast gates for spins, optical triggers for ions and photons, and more. It’s a practical approach: keep the timing digital and tight, then attach the right front‑end for the job.

Support For Superconducting, Spin, Photonic, And Ion Platforms

Superconducting, spin, photonic, and ion systems don’t behave the same, and that’s fine. The control stack lines up digital timing (SFQ and cryo‑logic where it helps) with the right analog or optical interface at the edge.

- Superconducting qubits: Picosecond‑class digital timing drives microwave and flux pulses near the fridge. Readout uses resonators; digitization and multiplexing sit close to reduce cabling.

- Silicon spin qubits: Mixed RF/microwave control plus very stable DC bias. Local cryo electronics trim drift and shrink the wire count. Readout supports SET/quantum‑dot sensors.

- Photonic processors: High‑speed drivers for modulators and switches, plus time‑tagging for single‑photon events. Works with room‑temp photonics and cryogenic detectors.

- Trapped ions: Deterministic digital triggers for AOMs/EOMs and RF trap drives. Low‑latency time‑to‑digital capture supports state detection via fluorescence counts.

Modality table (typical conditions vary by vendor and design):

| Modality | Typical environment | Primary controls | Common readout | Interface hooks |

|---|---|---|---|---|

| Superconducting | ~10–20 mK cryostat | GHz microwave, flux bias | Dispersive resonator | SFQ‑driven pulse synth, cryo MUX, fast digitizers |

| Silicon spin | ~10–100 mK cryostat | ESR microwave, DC gates | Spin‑to‑charge via SET/QPC | Low‑noise bias DACs, RF gating, on‑chip demod |

| Photonic | Room temp to cryo (detectors) | EO modulator drive, switch control | Single‑photon detection | SerDes drivers, time‑taggers, SNSPD readout links |

| Trapped ions | UHV, room temp or cryo | Laser pulse timing, RF trap drive | Fluorescence counts | Deterministic digital triggers, counter/timer blocks |

Adaptable Interfaces For Neutral Atoms And Topological Qubits

Neutral atoms and topological qubits sit at opposite ends of the lab setup spectrum—one laser‑heavy, the other fridge‑heavy—but both still want precise timing and stable feedback.

- Neutral atoms: The system outputs clean, jitter‑tight digital triggers for AOMs/EOMs, intensity servos, and camera gates. Real‑time branching lets you switch pulse plans on the fly based on mid‑circuit measurement.

- Topological qubits: Similar to superconducting stacks—flux/charge biasing, microwave drive, and parity‑style readout. Cryogenic digital logic helps push fast feedback without hauling signals up and down the fridge.

- Shared tooling: The same scheduling and calibration software compiles to different front‑ends, so teams keep their workflow while changing the hardware back‑end.

What this buys you:

- One timing model, many physical interfaces.

- Lower wiring overhead by pushing control and MUX closer to the device.

- Faster feedback loops for error detection and resets.

Optimization Within Existing Enterprise Infrastructure

You don’t rip out your stack just to try a new qubit. SEEQC’s software and firmware (including Prism) aim to fit in next to the systems you already run.

- APIs match common lab control patterns (pulse schedules, param sweeps, calibration routines) and link to containerized services for scheduling and data logging.

- Hybrid pipelines tie QPU control to CPUs/GPUs for decoding and optimization. That helps real‑time error correction where bandwidth and latency matter.

- Fleet ops: Versioned configs, rollback, and health metrics make it feel like running regular services, not a bespoke science project.

Practical optimization loop:

- Map the modality’s control graph (gates, ramps, readout) to a digital timing plan.

- Compile to SFQ/cryo‑logic blocks and the right front‑end drivers (microwave, RF, optical).

- Co‑simulate pulses and readout paths; push to hardware; auto‑tune with closed‑loop calibration.

- Stream metrics (latency, energy per operation, SNR) to your monitoring stack; iterate.

The result is a setup that can host different qubit types, try new error‑reduction tricks, and keep using the compute and DevOps tools your team already trusts.

The Road Ahead for Quantum Computing

So, SEEQC is really changing the game when it comes to building quantum computers. They’re making these super-cold chips that work right alongside the quantum parts, which is a big deal. It’s like they’re figuring out how to connect the really complicated quantum stuff to the computers we already use, but in a way that’s faster and less of a headache. They’re using silicon, like regular computer chips, but in a totally different way. It’s still early days, but the idea is that this could make quantum computers much easier to build and use for real problems. It’s a step towards making quantum computing something we can actually work with, not just something we read about.